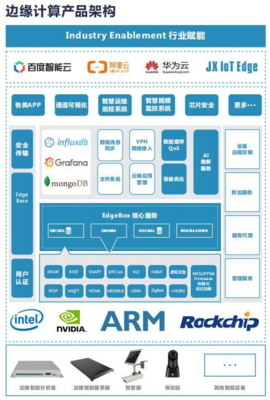

在人工智能的浪潮中,邊緣計算正日益成為推動AI應用落地的關鍵力量。百度推出的EdgeBoard邊緣AI計算盒,作為專為邊緣場景設計的硬件平臺,其核心驅動力在于對卷積神經網絡(CNN)的高效、低功耗部署。本文旨在剖析EdgeBoard中CNN架構的實現,并深入探討其背后的矩陣運算奧秘。

一、EdgeBoard與邊緣AI的挑戰

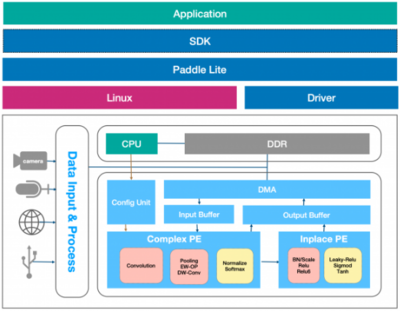

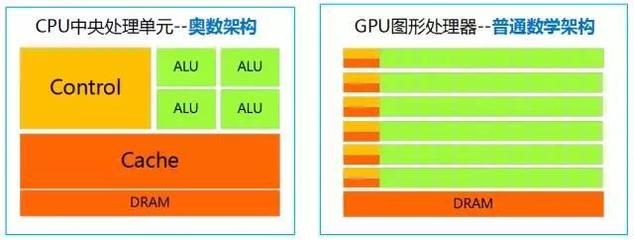

EdgeBoard的核心使命是將復雜的AI模型,尤其是CNN,從強大的云端服務器遷移至資源受限的邊緣設備(如攝像頭、無人機、工業網關)。這面臨著三大核心挑戰:計算能力有限、內存帶寬緊張、功耗要求苛刻。傳統的通用處理器(CPU)難以勝任,因此EdgeBoard通常采用定制化的FPGA或ASIC芯片,通過硬件級的并行優化來應對這些挑戰。

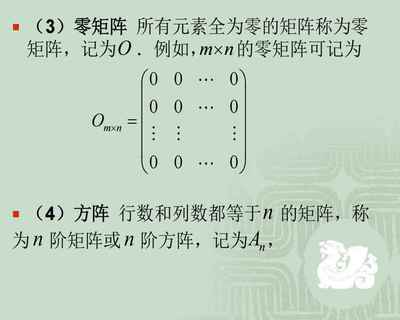

二、CNN架構的核心:卷積的矩陣化

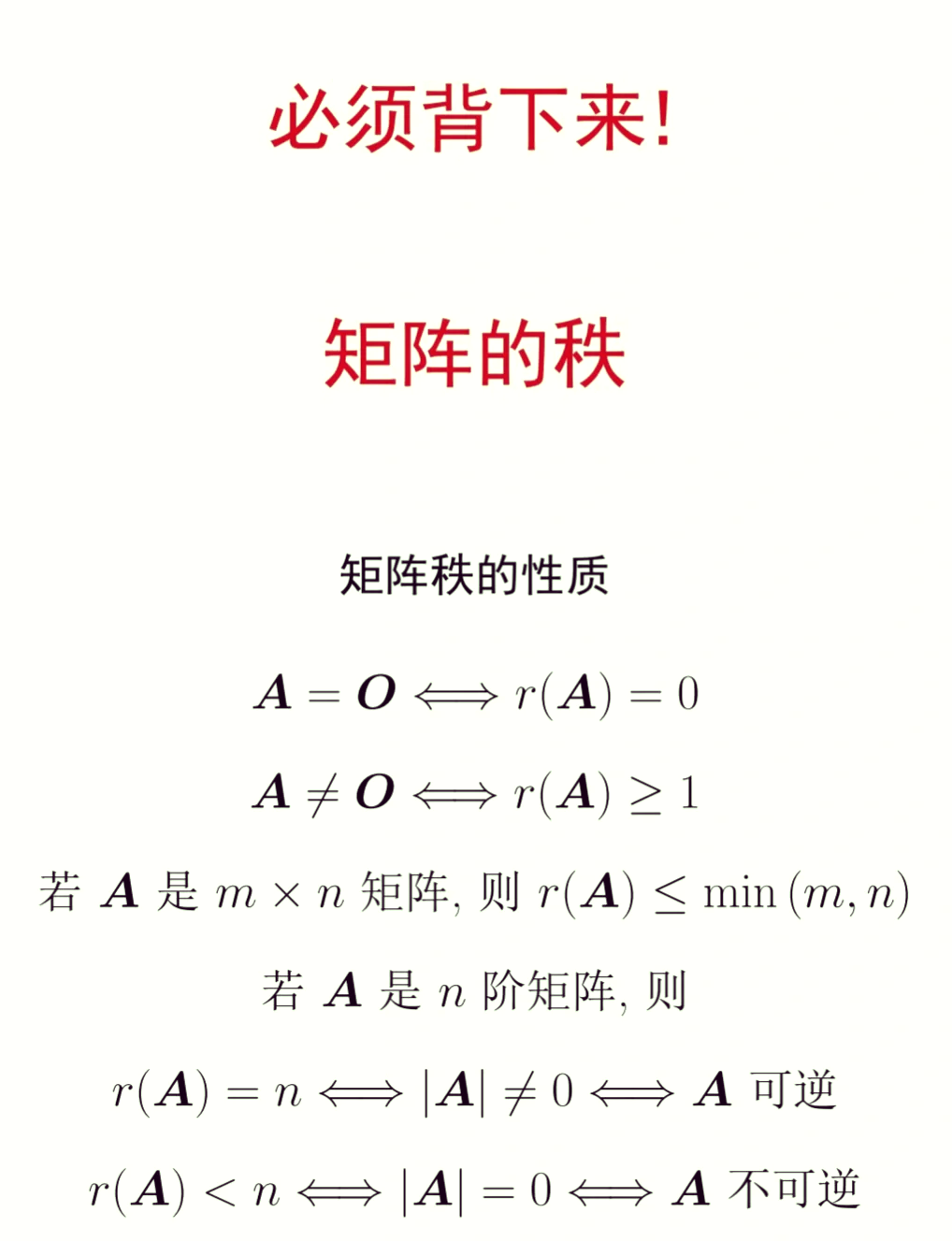

卷積神經網絡之所以在視覺任務中表現卓越,卷積層功不可沒。其核心操作是卷積核在輸入特征圖上的滑動窗口計算。在硬件實現中,尤其是為了發揮并行計算優勢,將卷積運算轉化為大規模的矩陣乘法(GEMM)是至關重要的優化策略。

- Im2Col(Image to Column)變換:這是最經典的優化方法。它將輸入特征圖的每個局部感受野(與卷積核大小對應)展開(im2col)成矩陣的一列,將多個卷積核的權重展開成矩陣的行。如此,復雜的卷積操作便轉化為了兩個矩陣(展開后的輸入矩陣與權重矩陣)的乘法。EdgeBoard的硬件設計會深度優化這一變換過程,減少數據搬運開銷。

- Winograd算法:對于較小的卷積核(如3x3),Winograd算法可以通過減少乘法次數來進一步提升計算效率。EdgeBoard的編譯器或硬件邏輯可能會在特定層智能地選擇使用Winograd算法來加速。

三、EdgeBoard的硬件架構如何加速矩陣運算

EdgeBoard的硬件(以FPGA方案為例)并非通用處理器,其設計緊緊圍繞著高效執行CNN的矩陣/向量運算。

- 高度并行化:FPGA可以配置大量的并行計算單元(PE),每個PE負責處理矩陣乘法中的一個或一組運算。這些PE可以同時工作,極大地提升了卷積(即矩陣乘法)的吞吐量。

- 數據流架構與片上緩存:為了緩解內存帶寬壓力,EdgeBoard硬件采用精細的數據流設計。通過層次化的片上緩存(Buffer),將輸入特征圖、權重和中間結果盡可能地保留在芯片內部,實現數據的“重用以減少訪存”,這是提升能效比的關鍵。

- 定制數據精度:EdgeBoard支持INT8等低精度量化。將FP32模型量化為INT8后,矩陣乘法的操作數位寬大幅降低,這意味著同樣的硬件資源可以處理更多的并行計算,同時內存占用和帶寬消耗也顯著下降,非常適合邊緣場景。

四、從模型到部署:編譯與優化

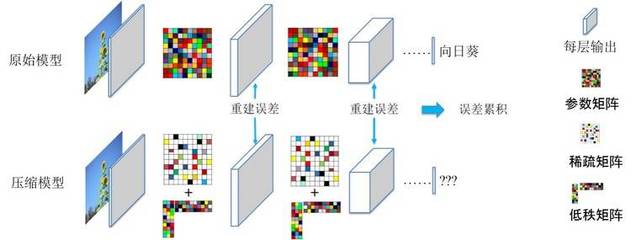

將訓練好的CNN模型部署到EdgeBoard上并非簡單的移植,需要經過其專用工具鏈的編譯與優化。這個過程可以理解為對CNN計算圖的“硬件友好型重構”。

- 計算圖優化:工具鏈會進行算子融合(如將Conv、BN、ReLU融合為一個計算單元)、層間調度優化,以減少中間數據的讀寫。

- 內存布局優化:根據硬件特性,將矩陣數據在內存中的排列方式(如NCHW或NHWC)調整為最優格式,以最大化數據訪問的局部性和并行性。

- 指令生成:優化后的計算圖被編譯為可以在EdgeBoard硬件上高效執行的指令序列,精確控制每一個計算單元和數據流。

五、與展望

對EdgeBoard中CNN架構的剖析,揭示了邊緣AI部署的核心邏輯:通過算法(矩陣化變換、量化)與硬件(并行PE、數據流、定制存儲)的協同設計,將CNN的計算密集部分——卷積及其背后的矩陣運算——極致優化。這不僅是一個工程問題,更是算法、編譯器和硬件架構的深度耦合。

隨著神經網絡架構的演進(如Vision Transformer的出現),EdgeBoard這類邊緣計算平臺也將持續進化,但其核心思想——針對核心計算模式進行軟硬件一體的定制化加速——將始終是突破邊緣算力瓶頸的不二法門。從矩陣運算的微觀優化到系統級的部署,EdgeBoard為我們展示了AI真正走入萬物互聯時代的堅實技術路徑。